Sardis Technologies

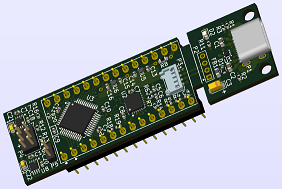

ST68F50-ST65F51 ACIA USB-FIFO Module

The ST68F50-ST65F51 ACIA USB-FIFO Module can replace a 6850 ACIA or 6551 ACIA chip in any system -- just remove the ACIA chip and plug this new module into the IC socket. The module emulates the 6850 or 6551 register set closely enough that most software can use the module without any changes. But it provides direct USB connection to a modern host PC, much faster communication, and supports automatic hardware flow control that eliminates data overrun and loss even at maximum speed.

ST68F50-ST65F51 version 1.0 prototype features:

- one 0.78"x2.58" (19.8mm x 65.5mm) 4-layer board with most components on one side -- can be separated into two boards

- 24-pin or 28-pin DIP header to plug into IC socket

- USB 2.0 Type-C connector, SMT but with thru-hole tabs

- Molex Pico-EZmate 4-pin 1.2mm pitch connector (only used if the USB Connector board is separated from the main module board)

- FTDI FT240XQ USB-FIFO in a QFN-24 package, supports data transfer rates up to 1 Mbyte/s (but will be limited to less than that by the driver software)

- Lattice ispMACH 4064ZE CPLD in a TQFP-48 package, with 5V-tolerant pins

- TI TLV740P +3.3V LDO and +1.8V LDO in tiny 1x1mm X2SON packages

- supports bus speeds up to 2 MHz (or even faster?)

- 2x3 2mm male header to connect to external JTAG programmer

- very low power (typically ??mA @ +5V from the IC socket)

This module prototype can be assembled and programmed to emulate either a 24‑pin 6850 ACIA (616KB .pdf) or a 28-pin 6551 ACIA (1.0MB .pdf), or used as a general-purpose breakout board for the Lattice ispMACH 4064ZE CPLD. The small USB connector board can either remain attached to the main board, or be cut off and the two boards re-connected with a 4-conductor cable, to provide more flexibility.

I do not plan to manufacture and sell this module. Instead, I will publish the complete set of documentation on this web page: KiCad schematics and PCB layout files, Gerber files, BOM, CPLD design and programming files, and assembly instructions. Ideally this prototype design would be modified into separate optimized 24-pin 6850 and 28-pin 6551 modules before being put into volume production.

The Lattice ispLEVER Classic CPLD design software requires a licence, which used to be free, but now is rather expensive at U$599 or more for 12 months. However, if you use the provided CPLD designs as-is, you don't need the design software, and can use the free Lattice Diamond Programmer Standalone application to program the CPLD with the .jed files I will supply. I'm hoping that the OpenOCD and/or openFPGALoader programs will also be able to program the CPLD via the on-board USB-FIFO chip, eliminating the cost of an external JTAG programmer.

|

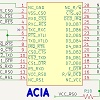

ST68F50-ST65F51 v1.0 schematics. (Preliminary, 2026-Apr-02) (699KB .pdf) |

|

ST68F50-ST65F51 v1.0 design and production files. (Preliminary, 2026-Apr-01, created with KiCad 7.0.9) (209KB .zip) |

Progress History (updated 2026-Apr-02)

In October 2020 I first had the idea to design a card for the SS-30 bus that would use an FTDI FT240X USB-FIFO chip for use with DriveWire or FLEX-OS9-Net or my DSKdrv/DSKserv software, to access disk images on a remote host PC at higher speeds than what a serial port based on the 6850 ACIA could provide. (A 1 MHz 6850 is limited to a 16x clock speed of 800kHz, so its fastest "standard" data rate is only 38400 bps.) Later I considered using an RP2040 microcontroller instead of the FTDI chip, but abandoned that idea when I realized it involved software development using too many new (to me) tools that would take lots of time to learn.

Then in May 2024 I got the idea to rather build a 24-pin module that would replace just the 6850 ACIA chip itself on any existing board. This would allow it to be used in more systems than just ones having an SS-30 bus.

On 2026-Mar-16 I started designing this new module, using KiCad. I soon realized it would be possible to emulate either a 6850 or 6551 with the same board. Ten days later I had finished an initial version of the schematics and PCB layout. Over the following several days I added features to allow it to also be used as a general-purpose breakout board for the Lattice ispMACH 4064ZE CPLD, and to test using the onboard USB-FIFO chip to program the CPLD using openFPGALoader or OpenOCD.

The next step will be to design the CPLD logic. I had planned to use the ABEL design language rather than VHDL or Verilog, as ABEL is what I already used several years ago for my UFDR floppy disk reader project. But I changed my mind, and will now use Verilog.

I will probably first test this module on my old Microware SC1-B SS-30 card plugged into my SwTPc system.

Last revised 2026-Apr-02 13:43 PDT.

Copyright 2018- David C. Wiens.

Home My SwTPc System Contact Site map