ST-2900 CPU

Assembly Instructions and User's Manual

Copyright 1984 by David C. Wiens All rights reserved

Sardis Technologies 2261 East 11th Avenue Vancouver, B.C. Canada V5N 1Z7

Although much effort has been made to ensure the accuracy of the hardware, software and documentation, David C. Wiens and Sardis Technologies disclaim any and all liability for consequential damages, economic loss, or any other injury arising from or on account of the use of, possession of, defect in, or failure of the supplied material.

This manual last revised September 7, 1984. (and May 14, 1986)

# ST-2900 CPU Board Assembly Instructions

| [] If you purchased a partially assembled board, skip this section and proceed to the section "Getting Started".                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [] Read Appendix A and decide on which configuration you want.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| [] Use a drill to enlarge the four mounting holes, if necessary. If you are also building the FDC board, drill both boards together to ensure the holes will line up.                                                                                                                                                                                                                                                                                                                                                                           |

| [] Carefully check both sides of the board visually for any incomplete etching, foil "bridges" or "breaks".                                                                                                                                                                                                                                                                                                                                                                                                                                     |

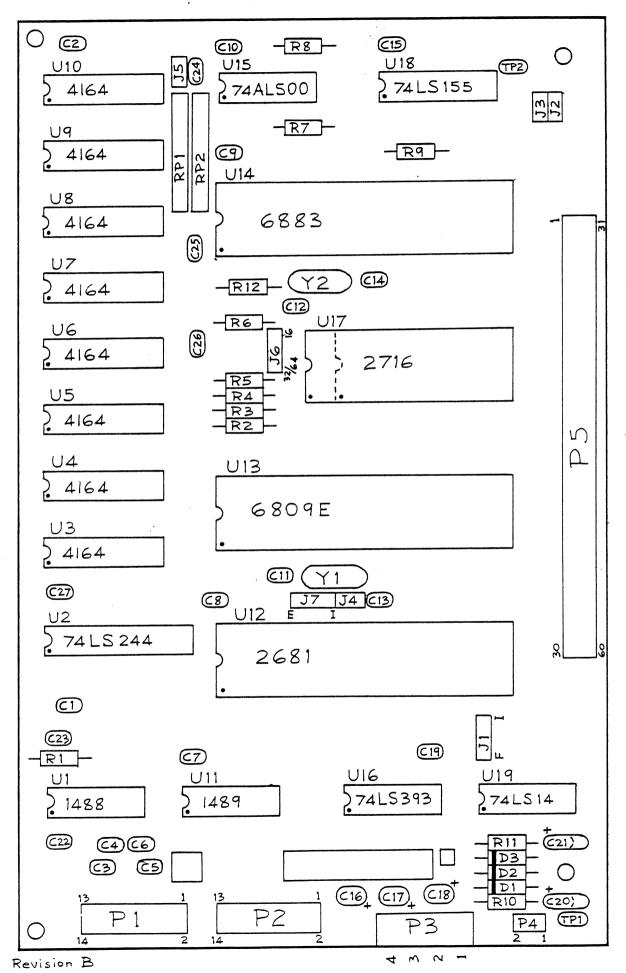

| [] Note whenever the component markings on the board are not entirely clear, refer to the component layout elsewhere in this manual.                                                                                                                                                                                                                                                                                                                                                                                                            |

| [] Use an ohmmeter between pins 1 and 4 of connector P3 to verify that there are no shorts between ground and +5vdc traces.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| [] Install and solder all IC sockets. If they have a notch or indentation at one end, orient them to match the "half circle" marking at the end of each IC outline on the board. Note, that if you are using a 24 pin socket for U17 to "lower justify" it in the 28 holes provided, ie. leave the holes in the PCB for pins 1, 2,27,28 open, and the "half circle" exposed.                                                                                                                                                                    |

| [] Install and solder all resistors, including RP1 and RP2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Install and solder all capacitors. Be especially careful with C16,C17,C18,C20,C21 the "+" on the PC board indicates the side where the positive lead should go. A tantalum capacitor installed backwards can explode. Note that C20 and C21 each have 3 holes provided instead of only 2 this gives you a choice of .100" or .200" lead spacing. One lead must be inserted into the nole with the "+" beside it; the other lead can be inserted into either of the two other holes. C17 is not marked on the board, but is between C16 and C18. |

| Install and solder connectors P1 and P2 and P4. If they are a tight fit, use a small screwdriver (or wirewrapping tool over the posts) to force them in. Be careful the posts of some connectors have very sharp points.                                                                                                                                                                                                                                                                                                                        |

| I] If you will be using male header strips for the 3 wiring blocks (see Appendix E), install and solder them now.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| [] Install and solder the 3 pin header strips for jumpers J1 and J6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ] Install and solder the 2 pin jumpers J2,J3,J5. If you don't anticipate thanging these settings, just solder wire jumpers across.                                                                                                                                                                                                                                                                                                                                                                                                              |

| Install and solder test points TP1 and TP2. These can be made by bending a length of bare wire into a loop:                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| [] If you will not be using crystal Y1, see the instructions in Appendix A. Otherwise solder a jumper wire across J4, and another one at J7 from the center hole to the "I" hole.                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [] Install and solder the power connector P3. If the connector you are using has square pins, you might have to round the inside corners of pins 1 and 4 so they fit into the holes.                                                                                                                                   |

| [] Install and solder all diodes. Note that the banded ends should be oriented to match the arrow-head and bar symbol on the diode outlines on the PC board. In other words, the banded ends of the diodes should be closest to C18. Using a heatsink on the diode leads while soldering reduces the chance of damage. |

| [] Install and solder connector P5. NOTE this connector is inserted into the back side of the board and soldered on the top side of the board. With so many pins, it might take quite a bit of wiggling to force the connector into blace.                                                                             |

| Other components  T P5                                                                                                                                                                                                                                                                                                 |

| [] Install and solder the crystals. To be on the safe side, use a piece of electrician's tape to insulate the crystal case from the PC board. Be careful not to overheat the crystals while soldering.                                                                                                                 |

| Double check your work, especially looking for missed or improperly soldered joints or accidental solder bridges.                                                                                                                                                                                                      |

[] You can now proceed to the section entitled "Getting Started -- Partially

## Getting Started -- Partially Assembled CPU Board

As sembled CPU Board".

[] NOTE -- static electricity can damage MOS integrated circuits. Even a static electricity charge too weak to feel can cause problems, and the damage, if it merely weakened the chip, might not cause the chip to fail until weeks or months later. While handling any MOS IC's you should ground your body and all tools that will touch the IC leads. Use a 1 Megohm resistor in series between you and ground to protect yourself against dangerous shocks. Also, handle the assembled board with care -- just because the IC's have been installed in their sockets doesn't make them immune to static electricity. Better safe than sorry.

| [] Make up a cable and connector from your power supply to connector P3. Note that pin 1 of P3 is the one closest to connector P4. If the connectors you are using don't physically prevent you from plugging the socket into P3 backwards or one pin "off", make sure to mark pin 1 of both plug and socket.                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [] At this point all IC's should be removed from the board. Connect the CPU board to the power supply and turn it on. Measure the supply voltages at several points.  Eg. U1 pin 1 should be between -10.8 vdc and -13.2 vdc                                                                                                                 |

| U1 pin 14 " " +11.4 vdc and +12.6 vdc<br>U15 pin 14 " " +4.75 vdc and +5.25 vdc                                                                                                                                                                                                                                                              |

| [] Turn the power supply off and disconnect from CPU board, then short pins 2, 3, and 4 to pin 1 at connector P3 to discharge the capacitors.                                                                                                                                                                                                |

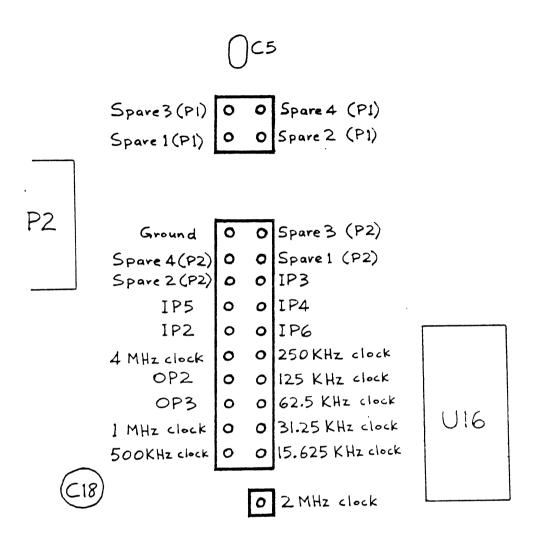

| [] If you will be running the FLEX or STAR-DOS Level I operating systems, use a jumper wire to connect the "IP2" pin to the "15.625 KHz" pin at the main wiring block (see Appendix E).                                                                                                                                                      |

| [] Put shorting blocks on the jumpers as necessary for your particular configuration. See Appendix B for a description of all jumpers.                                                                                                                                                                                                       |

| [] Install all IC's (but NOT the 8 RAM chips, U3-U10) into their sockets. Be sure you plug them in the right way. Double check against the component layout diagram. If you are inserting a 2716 or 2732 into a 28 pin socket at U17, the IC should be "lower justified", ie. leave pins 1,2,27,28 of the socket open.                       |

| [] Make up the cable to connect P1 to the terminal (see Appendix D), and hook it up.                                                                                                                                                                                                                                                         |

| [] Hook up the reset switch. The two pins of connector P4 sould go to a SPST momentary contact (normally open) switch.                                                                                                                                                                                                                       |

| [] Follow the instructions in Appendix C of the ST-MON 2.04 manual regarding configuring the serial port and terminal for data bits and parity.                                                                                                                                                                                              |

| [] Connect the CPU board to the power supply, but don't turn it on yet.                                                                                                                                                                                                                                                                      |

| [] Turn on the CRT terminal and wait until the cursor is visible.                                                                                                                                                                                                                                                                            |

| [] Now power up the CPU board. After about 2 seconds you should see "M2CW?" displayed on the terminal. Turn off the CPU power supply and the terminal. If you didn't see the "M2CW?" message, follow the instructions in the "Trouble Shooting Hints" section until you get that message. Don't go onto the next step until this step works. |

| [] Now install the 8 RAM chips (U3-U10) into their sockets, making sure to plug them in the right way.                                                                                                                                                                                                                                       |

| [] Power up the terminal and then the CPU board as before. This time all you should see is a "CW?" message. Respond by typing the letter "C", after which you should get the ST-MON copyright message and command prompt.                                                                                                                    |

| []  | Momer | ntarily | depress | the   | reset  | switc   | :h. / | After | approx. | 3 | seconds | you | should |

|-----|-------|---------|---------|-------|--------|---------|-------|-------|---------|---|---------|-----|--------|

| see | the   | "CW?"   | message | agair | n. Res | s po nd | wi th | "C".  |         |   |         |     |        |

[] Before proceeding, thoroughly check out the operation of the CPU board. See the ST-MON User Manual for the various commands available.

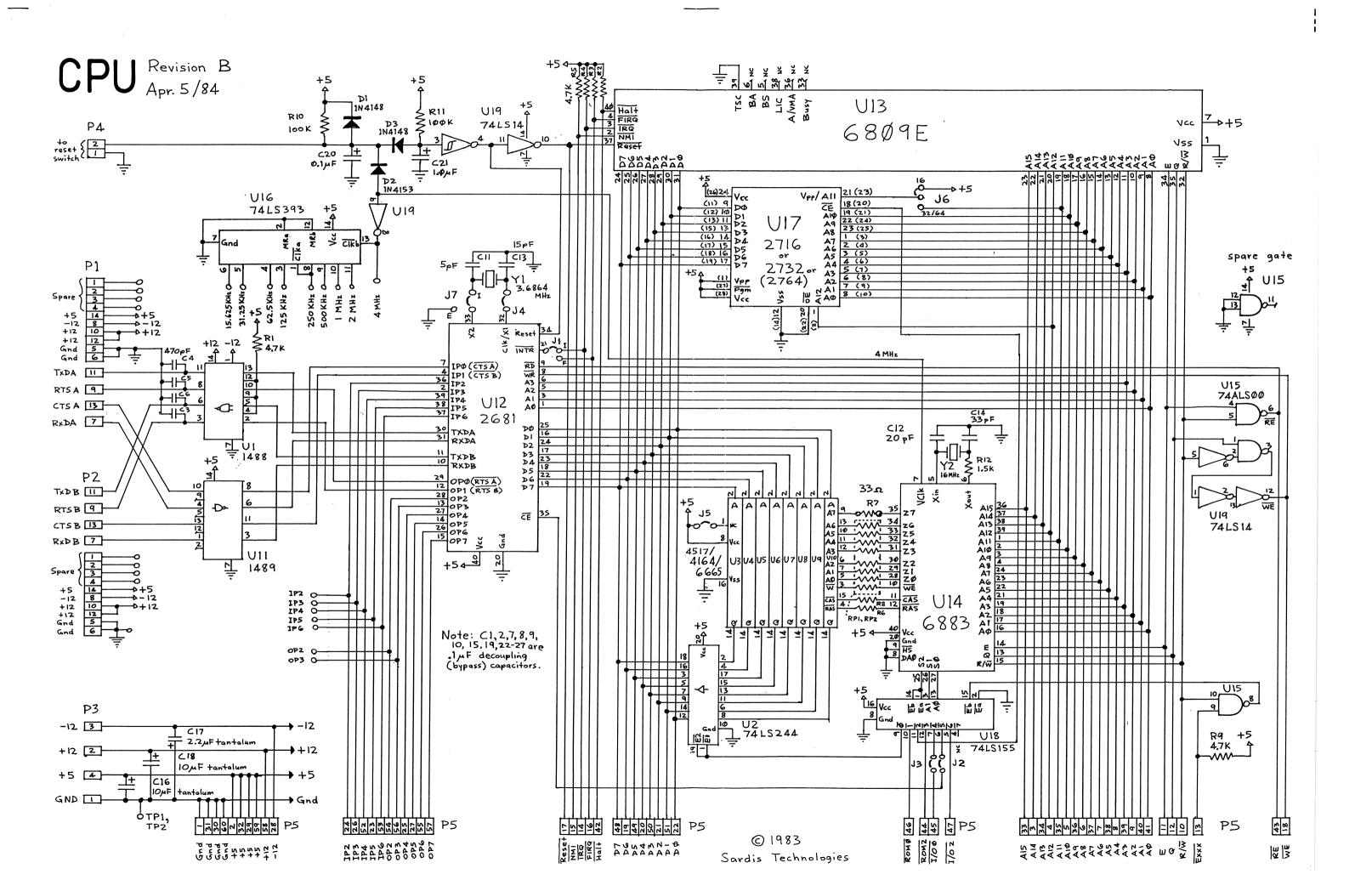

## Theory of Operation

Two integrated circuit chips are mostly responsible for the ST-2900's architecture -- the 6809E and 6883.

The 6809E microprocessor (U13) does the actual processing.

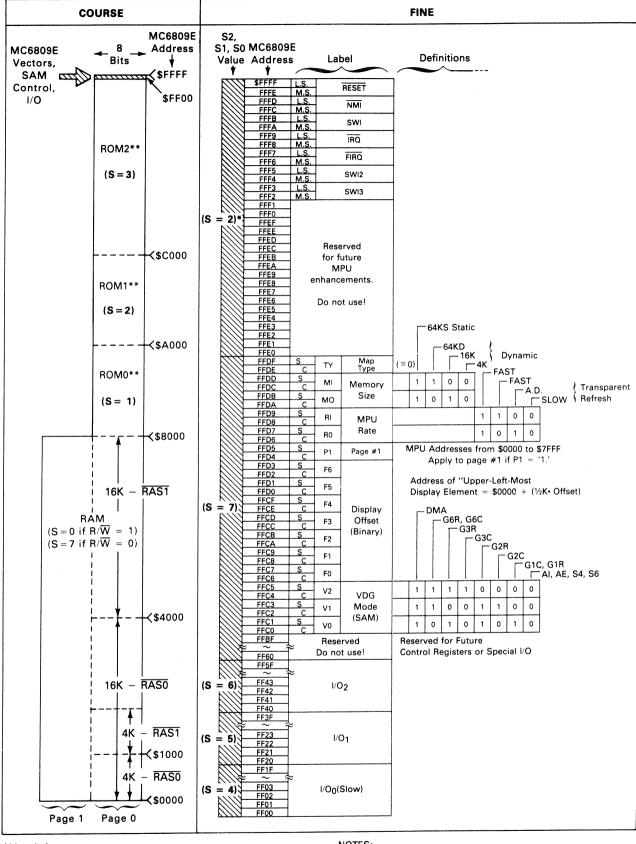

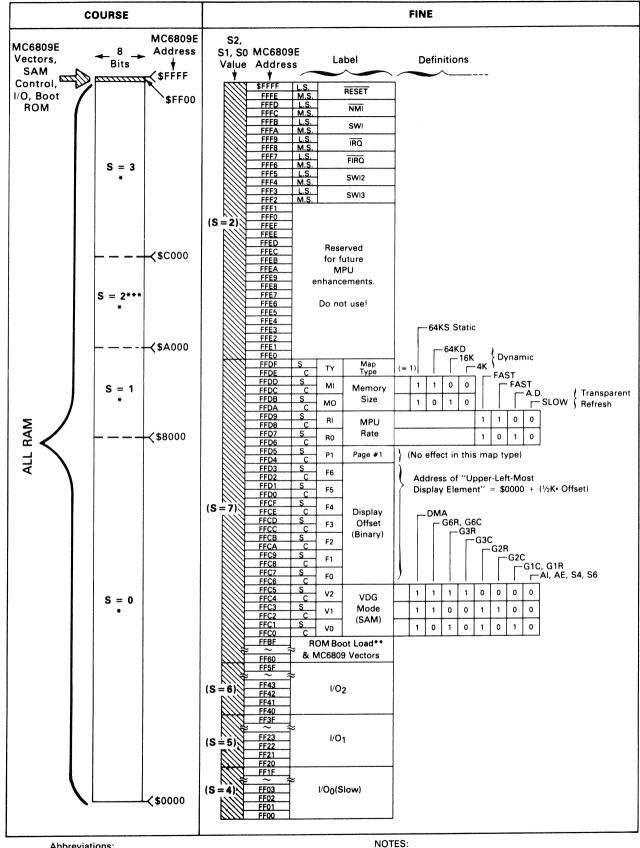

The 6883 Synchronous Address Multiplexor (SAM) (U14) takes care of all the timing/refreshing/multiplexing of the dynamic RAM as well as playing a major part (together with U18) in system address decoding. A few selected pages from Motorola's data sheet are included at the end of this manual.

Integrated circuit U17 is an EPROM of either 2K, 4K, or 8K bytes. The program stored in it gains control whenever the system is powered up or after the RESET switch is pressed.

Integrated circuits U3-U10 provide either 16K (16,384) or 64K (65,536) bytes of read/write memory. Since these chips are organized as 16Kx1 or 64Kx1, one 8 bit byte is stored with one bit in each of the 8 chips, with the high order bit in U3 and down to the low order bit in U10.

U2 is a buffer which, when the EXXX line (pin 13 of P5) is pulled low, isolates the RAM outputs from the data bus to allow a user provided device to occupy part of the RAM's normal address space.

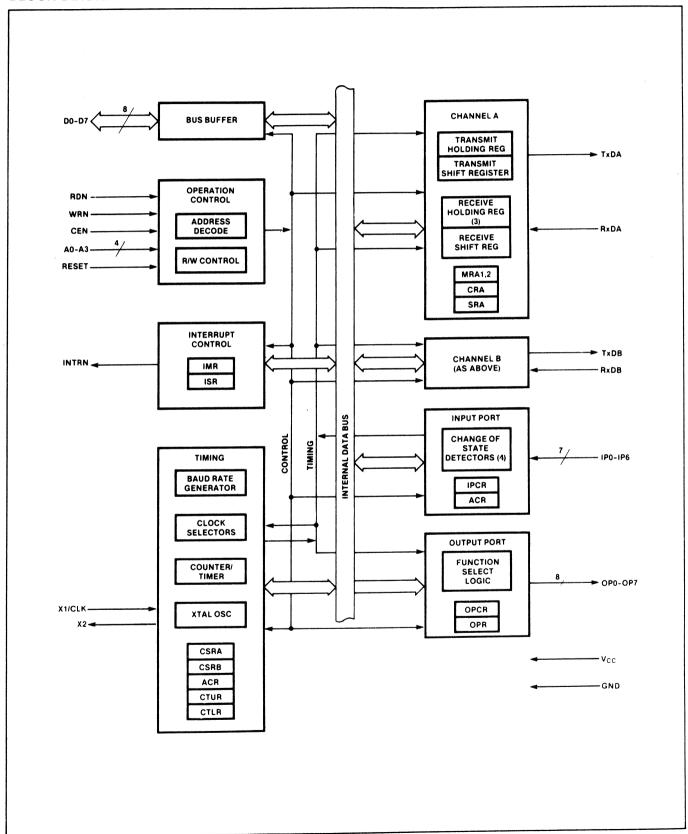

Integrated circuit U12 implements two asynchronous serial I/O ports which are buffered to RS-232 levels by U1 and U11. The entire Signetics data sheet (except for pages 1 and 2) is included at the end of this manual.

Integrated circuit U16 divides down a 4 MHz clock signal to provide 9 various clock frequencies.

Two gates of U19, along with some resistors, capacitors, and diodes, generate three different reset signals whenever the system is powered up or the reset switch is pressed.

### Trouble-shooting Hints

The first step is to double check the settings of jumpers J1-J7. Refer to the component layout diagram for the orientation of J2 and J3.

The second step is to double check and triple check that all components are in the right locations, and that they are oriented properly. Also make sure that the pins of all integrated circuits were correctly inserted into the sockets; sometimes a pin gets bent underneath the IC body.

If everything looks OK so far, carefully inspect all of the solder joints on the board, looking for missed connections, "cold" solder joints, and solder "bridges".

Use a voltmeter to measure the +5, +12, -12 volt supplies at each chip -- use the schematic as a guide. See the section "Getting Started ..." for the acceptable voltage ranges. Test points TP1 and TP2 provide a convenient connection to ground.

Double check your connections between connector P1 and your terminal. Note that the terms TxData/RxData/RTS/CTS are named from the 2681 DUART's point of view, not from the terminal's. See Appendix D. The CTSA line must be connected, and should result in a logic O level at U12 pin 7.

When the reset switch is held down (or while pin 1 is shorted to pin 2 at connector P4) the voltage at U19 pin 10 should be  $\leq$  0.5 vdc. When not held down, the voltage should read  $\geq$  2.7 vdc.

If you still can't get the CPU board working, you will need access to an oscilloscope.

Check clock signals "E" and "Q".

Check the signals at the crystal oscillator circuit of U12. If not OK, try different values for C11 and C13 (between 0 and 20 pF).

Check the signal at U12 pin 30 -- after you have pressed the reset button, then released it, you should see a continuous logic 1 level. However, approximately 3 seconds after releasing reset you should see a very short burst of logic zeroes and ones, representing the output of the "CW?" message.

## Parts List - CPU Board

```

* U1

1488 RS-232 driver

* U2

74LS244 octal buffer

t* U3-U10 4164 or 6665 64Kx1 dynamic RAM (128 cycle refresh)

200 nsec. (or 4517 16Kx1) (Texas Instr. TMS4164 will NOT work)

* U11

1489 RS-232 receiver

2681 DUART (Signetics SCN2681AC1N40) (also made by Motorola)

* U12

* U13

6809E microprocessor

* U14

6883 SAM (synchronous address multiplexor) (74L5783 or 74L5785)

* U15

74ALSOO quad 2 input NAND (ALS preferred over LS)

* U16

74LS393 dual 4 bit binary ripple counter

2716 single supply (or 2732 or 2764) EPROM (450 nsec)

t* U17

* U18

74LS155 dual 2 line to 4 line decoder/demultiplexor

* U19

74LS14 hex inverter Schmitt trigger

3.6864 MHz crystal (HC-18 package)

t Y1

t Y2

16 MHz crystal

* D1,D3

1N4153 or 1N4148 diodes

* D2

1N4153 diode (1N4148 usually works, too)

4.7K ohm 1/4 watt resistors

R1-R5

R6-R8

33 ohm

11

R9

4.7K ohm

п

11

11

R10,R11 100K ohm

11

1.5K ohm

R12

RP1, RP2 33 ohm resistor network, 8 pin SIP, 4 isolated res.

C1,C2

.1uF or .15uF bypass capacitors

C3-C6

470pF capacitors

C7-C10

.1uF or .15uF bypass capacitors

t C11

5pF capacitor (may be omitted)

C12

22 pF capacitor

t C13

15pF capacitor

C14

33 pF capacitor

C15

.1uF or .15uF bypass capacitor

* C16

10uF tantalum capacitor 6.3vdc

* C17

2.2uF tantalum capacitor 16vdc

* C18

10uF tantalum capacitor 16vdc

C19

.1uF or .15uF bypass capacitor

* C20

.1uF capacitor (any type OK)

* C21

1.0uF capacitor (any type OK)

C22,C23 .1uF or .15uF bypass capacitors

C24-C27 .1uF or .15uF bypass capacitors

*

5 - 14 pin IC sockets

9 - 16 pin IC sockets

*

*

1 - 20 pin IC socket

t*

1 - 24 pin or 28 pin IC socket

3 - 40 pin IC sockets

```

```

14 pin (2 row x 7) .100" center male header with .025" square posts (eg. can be cut from 72 pin strip

P1.P2

such as AP Products 929836-01-36-R)

4 pin .156" center (.045" pin) connector

Р3

(eg. Molex 09-75-1048 plug and 09-50-3061 socket

plus two 15-04-0219 polarizing keys)

P4

2 pin .100" center male header (or Molex 22-05-3021

plug with 22-01-2027 socket)

60 pin (2 row x 30) .100" center male header

* P5

3 pin .100" center male header (eg. can be cut from

J1,J6

36 pin strip such as AP Products 929834-01-36-R)

2 pin .100" center male header

t J2.J3

2 pin .100" center male header

t J5

t

20 pin (2 row x 10) .100" center male header

(used as programming strip / wiring block)

4 pin (2 row x 2) .100" center male header

t

1 pin male header

```

\* these components must be oriented as marked on PCB t see appendix A for optional configurations

(Note - AP Products are also known

as Aptronics. AMP, Molex, etc.

also make similar connectors)

## APPENDIX A - Optional Configurations

### 1) Eliminating crystal Y1

You can eliminate the 3.6864 MHz crystal if you can tolerate running the CPU at slightly less than 1 MHz. If you will be using the FDC board with double density operation, do NOT use this option.

- a) substitute a 15 MHz crystal for Y2

- b) omit Y1, C11, C13

- c) wire J7 to the "E" position, not the "I" position

- d) leave J4 open

- e) add a jumper wire between the 4 MHz (has now become 3.75 MHz) wiring point and the lower pin (closest to C13) of J4. Refer to Appendix E.

Note that all the 9 clock frequencies from U16 are changed:

```

15.625 KHz becomes 14.648 KHz

31.25

29,297

11

11

62.5

58.594

" 117.188

11

125.0

250.0 "

" 234.375

500.0 "

" 468.75

1 MHz " 937.5

2 " " 1.875

. H

1.875 MHz

11

3.75

4

```

The baud rates generated by the 2681 DUART will be approx. 1.7% fast using this option, but that should cause no problems.

### 2) Socket for EPROM

If you will ever use a 2764 for U17, install a 28 pin socket. If only 2716's or 2732's will be used, a 24 pin socket will do.

### 3) 16K RAM / 64K RAM

Either 16K or 64K dynamic RAM chips can be used, but they must be 5 volt only supply types. Chips such as the 4116, which use 3 supply voltages, cannot be used. Also, 64K DRAM's that use a 256 cycle refresh (such as Texas Instruments) will not work. Note that ST-MON version 2.04 will only work with 64K.

### 4) J2/J3/J5/Wiring Block

You can either solder wires directly into these holes, or use header strips with jumper blocks or wire-wrap wires.

### APPENDIX B -- JUMPERS

### APPENDIX C -- MEMORY MAPS

After powerup or reset, but before the "CW?" prompt is answered:

```

0000-7FFF RAM

8000-9FFF ROM 0 (off board)

A000-BFFF on board EPROM (to A7FF if 2716, AFFF for 2732)

C000-FEFF ROM 2 (off board)

FF00-FF1F I/0 0 (off board)

FF20-FF3F 2681 DUART (FF30-FF3F mirrors FF20-FF2F)

FF40-FF5F I/0 2 (off board)

FF60-FFF1 various SAM registers

FFF2-FFFF interrupt vectors in EPROM

```

### After the "CW?" prompt is answered:

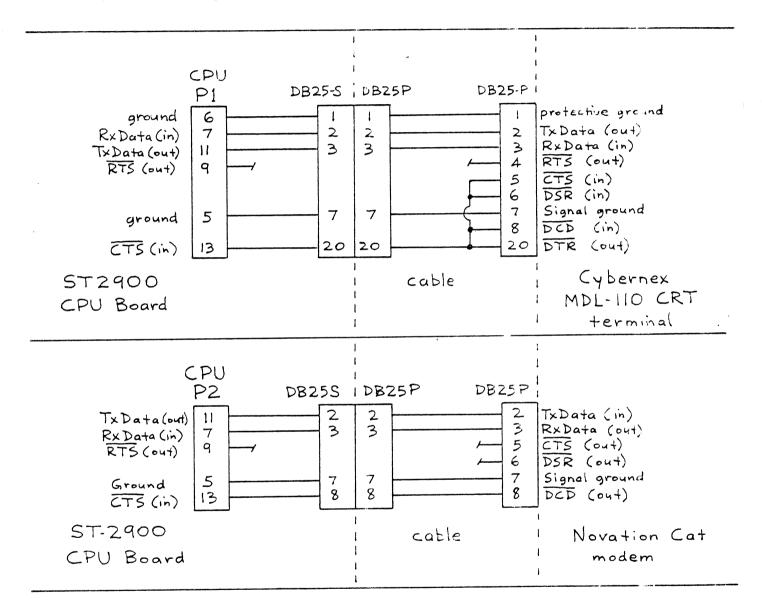

### APPENDIX D -- RS-232 Cabling

Many CRT's only require the signals on pins 2,3,7 on the DB-25 connector. Others require handshaking. In many cases some of the signals required by the CRT are generated via jumpers on the connector at the CRT end of the cable. A few examples are provided as a general guide. Note that the current version of ST-MON and the FLEX Conversion Package configure both serial ports to require asserting CTS in order to enable that port's transmitter.

## APPENDIX F - Expansion Connector P5

```

In/

Pin Out Name

Description

1

0 Ground

2

+5vdc

power supply

3

0 A14

address line from microprocessor

4

0 A12

11

н

5

0 A10

11

6

0 A8

7

0 A6

11

11

8

0 A4

11

11

11

0 A2

9

10

O R/\overline{W}

Read/Write control signal from microprocessor

E clock signal from 6883

11

0 E

12

0 Q

13

Ι

EXXX

when pulled low, disables access to RAM/EPROM

pull line low to generate IRQ interrupt

14

I

IRQ

15

NMI

NMI

Ι

11 11 11

Ħ

FIRQ

FIRO

16

Ι

17

0 Reset

master reset signal

WE

18

0

write enable

19

I/O D6

data bus line

20

I/O D4

н

21

I/O D2

Ħ

11

22

I/O DO

23

Ι

IP5

from DUART

24

IP2

Ι

11

п

25

0 OP4

26

IP3

Ι

11

27

0 OP5

28

-12vdc

0

power supply

29

0 +5vdc

30

0 Ground

31

0 Ground

32

0 + 5 v dc

power supply

33

0 A15

address line from microprocessor

34

A1 3

0

ш

0 A11

35

0 A9

36

37

0 A7

11

#1

0 A5

38

11

11

39

0 A3

11

.

40

0

A1

41

0

Α0

pull line low to halt the microprocessor

42

Ι

Halt

43

RE

Read enable

0

EPROM chip select ($COOO-$FEFF)

ROM 2

44

0

45

0

I/0 0

I/O chip select ($FF00-$FF1F)

ROM 0

EPROM chip select ($8000-$9FFF)

46

0

I/02

I/O chip select ($FF40-$FF5F)

47

```

| 48 | I/0 | D7     | data  | bus  |     |

|----|-----|--------|-------|------|-----|

| 49 | I/0 | D5     | II ·  | 11   | 11  |

| 50 | I/0 | D3     | н     | - 11 | 11  |

| 51 | I/0 | D1     | 11    | н    | 11  |

| 52 | I   | IP4    | from  | DUAF | RT  |

| 53 | I   | IP6    | н     | 11   |     |

| 54 | 0   | OP2    | 11    | 11   |     |

| 55 | 0   | 0P6    | 11    | 11   |     |

| 56 | Ō   | 0P3    | 11    | 11   |     |

| 57 | 0   | 0P7    | 11    | 11   |     |

| 58 | 0   | +12vdc | power | sur  | ply |

| 59 | 0   | +5vdc  | , II  | i    | 11. |

| 60 | 0   | Ground |       |      |     |

## APPENDIX G - Suggested Sources of Further Information

- 1) "6800 Software Gourmet Guide and Cookbook" by Robert Findley, published by Hayden, although not written for the 6809, has lots of useful subroutines that could be converted. Some of the chapter titles are "Conversion Routines" (incl. ASCII to/from Baudot), "Floating Point Routines", "Decimal Arithmetic Routines", and "Search and Sort Routines".

- 2) "The MC6809 Cookbook" by Carl. D. Warren, published by TAB, introduces the 6809 architecture and addressing modes, and includes descriptions of each machine instruction. A bonus is the complete assembly language source code of VTL-09 (Very Tiny Language for the 6809), a Tiny-BASIC-like interpreter that only occupies approx. 1K bytes!

- 3) "'68' Micro Journal", a monthly magazine for 6800/6809/68000 based systems, published by Computer Publishing Inc., 5900 Cassandra Smith, PO Box 849, Hixson, Tennessee, U.S.A. 37343. Current and back issues often contain source code listings of public domain programs.

- 4) "Microcomputing" magazine, formerly called "Kilobaud Microcomputing" or "Kilobaud", had many 6800 and 6809 articles from 1978 to 1982, especially during 1980/81.

- 5) Mountain View Press, Inc., P.O. Box 4656, Mountain View, California, U.S.A. 94040 (see their ads in BYTE magazine) have source listings for 6809 fig-FORTH available for approximately (US) \$15.

- 6) Several past issues of BYTE magazine have had articles dealing with the 6809. Some examples are March 1981 p.90, February 1979 p.32, and January 1979 p.14.

- 7) Assembler source code for a Fast Fourier Transform was published in the February '79 issue of BYTE, p.108. Although written for the 6800, it should be possible to convert to the 6809.

# CPU - Component Layout

P.O. BOX 20912 • PHOENIX, ARIZONA 85036

## SN74LS783/ MC6883 SN74LS785

#### Advance Information

#### SYNCHRONOUS ADDRESS MULTIPLEXER

The SN74LS783/MC6883 and SN74LS785 bring together the MC6809E (MPU), the MC6847 (Color Video Display Generator) and dynamic RAM to form a highly effective, compact and cost effective computer and display system.

The SN74LS783/MC6883 is designed to support 4K x 1, 16K x 1 and 64K x 1 (128 column refresh) dynamic RAMs. The SN74LS785 has been modified to support the above listed products as well as  $16K \times 4$  and  $64K \times 1$  (256 column refresh) dynamic RAMs. A further enhancement allows the LS785 to support low power dynamic ROMs (such as MCM68364) without additional logic.

- MC6809E, MC6800, MC6801E, MC68000 and MC6847 (VDG)

Compatible

- Transparent MPU/VDG/Refresh

- RAM size 4K, 8K, 16K, 32K or 64K Bytes (Dynamic or Static)

- Addressing Range 96K Bytes

- Single Crystal Provides All Timing

- Register Programmable:

VDG Addressing Modes

VDG Offset (0 to 64K)

**RAM Size**

Page Switch

MPU Rate (Crystal ÷ 16 or ÷ 8)

MPU Rate (Address Dependent or Independent)

- System "Device Selects" Decoded 'On Chip'

- Timing is Optimized for Standard Dynamic RAMs

- +5.0 V Only Operation

- Easy Synchronization of Multiple SAM Systems

- DMA Mode

#### TYPICAL SYSTEM BLOCK DIAGRAM **Device Selects** 8 TV Display Section SN74LS138 is Optional Clk S0-S2 SN74LS783/ DA0 A0-A15 Address **VDG** MC6883 HS MC6847 or ≈14 MHzh R/W SN74LS785 SAM Data DD0-DD7 To Q Z0-Z7 CAS **ROMs** MC6809E and I/O MPU SN74LS273 MC1372 RAS WE or RGB Ckt. **DYNAMIC RAM** Data D0-D7 Data 4K, 8K, 16K COLOR 32K or 64K (OR B/W) SN74LS244 **BYTES**

### SYNCHRONOUS ADDRESS MULTIPLEXER

LOW POWER SCHOTTKY

### MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise noted.)

| Rating                                    | Symbol           | Value        | Unit |

|-------------------------------------------|------------------|--------------|------|

| Power Supply Voltage                      | Vcc              | -0.5 to +7.0 | Vdc  |

| Input Voltage (Except Osc <sub>In</sub> ) | VI               | -0.5 to 10   | Vdc  |

| Input Current (Except Oscin)              | lı               | -30 to +5.0  | mA   |

| Output Voltage                            | ٧o               | -0.5 to +7.0 | Vdc  |

| Operating Ambient Temperature Range       | TA               | 0 to +70     | °C   |

| Storage Temperature Range                 | T <sub>stg</sub> | -65 to +150  | °C   |

| Input Voltage Osc <sub>in</sub>           | ViOscin          | -0.5 to VCC  | Vdc  |

| Input Current Oscin                       | loscin           | -0.5 to +5.0 | mA   |

#### **GUARANTEED OPERATING RANGES**

| Parameter                                  | Symbol | Min  | Тур | Max   | Unit |

|--------------------------------------------|--------|------|-----|-------|------|

| Supply Voltage                             | Vcc    | 4.75 | 5.0 | 5.25  | V    |

| Operating Ambient Temperature Range        | TA     | 0    | 25  | 75    | °C   |

| Output Current High<br>RASO, RAS1, CAS, WE | ЮН     |      |     | - 1.0 | mA   |

| All Other Outputs                          |        |      |     | -0.2  |      |

| Output Current Low<br>RASO, RAS1, CAS, WE  | lor    |      |     | 8.0   | mA   |

| VCIk                                       |        |      |     | 0.8   |      |

| All Other Outputs                          |        |      | -   | 4.0   |      |

## DC CHARACTERISTICS (Unless otherwise noted specifications apply over recommended power supply and temperature ranges.)

| Characteristic                                                                                                                                                                                                                                                                                                                                                            | Symbol                            | Min                                  | Тур                | Max                       | Units |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------|--------------------|---------------------------|-------|

| Input Voltage — High Logic State                                                                                                                                                                                                                                                                                                                                          | VIH                               | 2.0                                  |                    |                           | ٧     |

| Input Voltage — Low Logic State                                                                                                                                                                                                                                                                                                                                           | VIL                               |                                      |                    | 0.8                       | V     |

| Input Clamp Voltage<br>(VCC = Min, I <sub>in</sub> = -18 mA) All Inputs Except Osc <sub>In</sub>                                                                                                                                                                                                                                                                          | VIK                               |                                      |                    | - 1.5                     | V     |

| Input Current — High Logic State at Max Input Voltage $(V_{CC} = Max, V_{in} = 5.25 \text{ V}) \text{ VCIk Input}$ $(V_{CC} = Max, V_{in} = 5.25 \text{ V}) \text{ DA0 Input}$ $(V_{CC} = Max, V_{in} = 5.25 \text{ V}) \text{ Osc}_{ln} = \text{Gnd}) \text{ Osc}_{Out} \text{ Input}$ $(V_{CC} = Max, V_{in} = 7.0 \text{ V}) \text{ All Other Inputs Except Osc}_{ln}$ | Ιι                                | <br><br>                             | <br><br>           | 200<br>100<br>250<br>100  | μΑ    |

| Input Current High Logic State All Inputs Except VCIk, (V <sub>CC</sub> = Max, V <sub>in</sub> = 2.7 V) DA0 Osc <sub>in</sub> , Osc <sub>Out</sub>                                                                                                                                                                                                                        | ΙΗ                                |                                      |                    | 20                        | μΑ    |

| $\begin{array}{l} \text{Input Current } \textbf{— Low Logic State} \\ (\text{$V_{CC}$ = $Max$, $V_{in}$ = 0.4 V) DA0 Input} \\ (\text{$V_{CC}$ = $Max$, $V_{in}$ = 0.4 V) VCIk Input} \\ (\text{$V_{CC}$ = $Max$, $V_{in}$ = 0.4 V, $Osc_{in}$ = Gnd) $Osc_{Out}$ Input} \\ (\text{$V_{CC}$ = $Max$, $V_{in}$ = 0.4 V) All Other Inputs Except $Osc_{in}$} \end{array}$   | կլ                                | _<br>_<br>_<br>_                     | -<br>-30<br>-<br>- | - 1.2<br>- 60<br>- 8<br>4 | mA    |

| Output Voltage — High Logic State ( $V_{CC} = Min, I_{OH} = -1.0 \text{ mA}$ ) RAS0, RAS1, CAS, WE ( $V_{CC} = Min, I_{OH} = -0.2 \text{ mA}$ ) E, Q ( $V_{CC} = Min, I_{OH} = -0.2 \text{ mA}$ ) All Other Outputs                                                                                                                                                       | VOH(C)<br>VOH(E)<br>VOH           | 3.0<br>V <sub>CC</sub> - 0.75<br>2.7 | <del>-</del>       | _<br>_<br>_               | V     |

| Output Voltage — Low Logic State $(V_{CC} = Min, I_{OL} = 8.0 \text{ mA}) \text{ RAS0}, \overline{RAS1}, \overline{CAS}, \overline{WE}$ $(V_{CC} = Min, I_{OL} = 4.0 \text{ mA}) \text{ E, Q Outputs}$ $(V_{CC} = Min, I_{OL} = 0.8 \text{ mA}) \text{ VClk Output}$ $(V_{CC} = Min, I_{OL} = 4.0 \text{ mA}) \text{ All Other Outputs}$                                  | VOL(C)<br>VOL(E)<br>VOL(V)<br>VOL | _<br>_<br>_<br>_                     | _<br>              | 0.5<br>0.5<br>0.6<br>0.5  | V     |

| Power Supply Current                                                                                                                                                                                                                                                                                                                                                      | Icc                               |                                      | 180                | 230                       | mA    |

| Output Short-Circuit Current                                                                                                                                                                                                                                                                                                                                              | los                               | 30                                   |                    | 225                       | mA    |

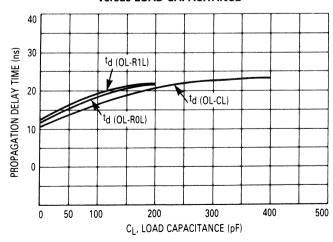

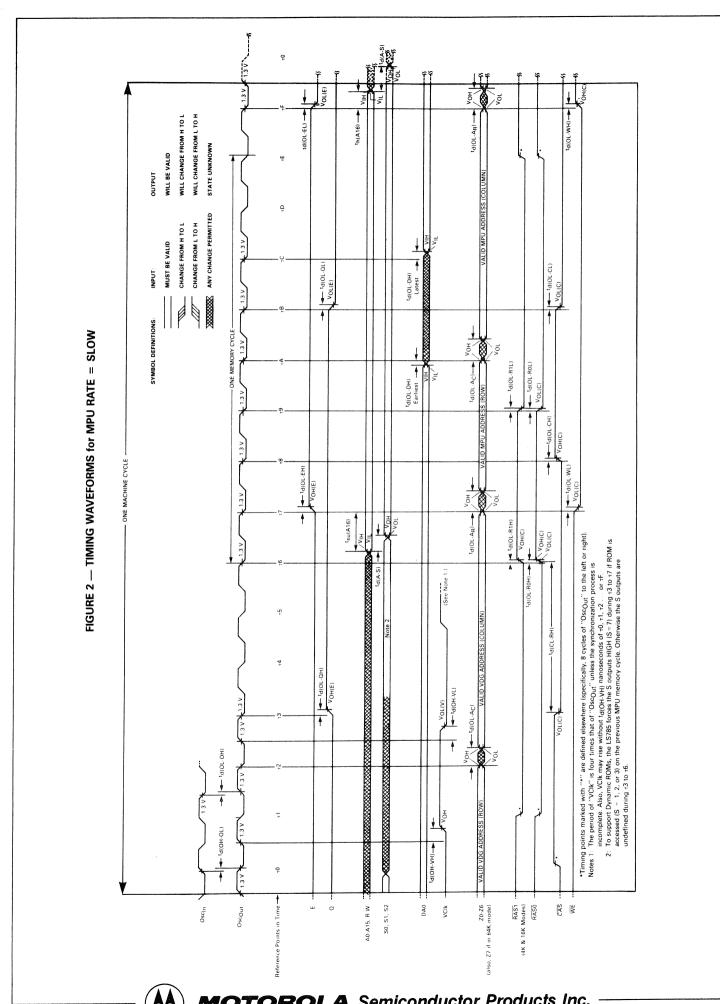

**AC CHARACTERISTICS** (4.75  $V \le V_{CC} \le 5.25 \text{ V}$  and  $0 \le T_A \le 70^{\circ}\text{C}$ , unless otherwise noted).

| Characteristic                                                                                                                                        |                            | Symbol                                         | Min      | Тур          | Max      | Units |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------|----------|--------------|----------|-------|

| Propagation Delay Times<br>(See Circuit in Figure 9) Oscillator-In 📜 to<br>Oscillator-In 🗩 to                                                         |                            | <sup>t</sup> d(OL-OH)<br><sup>t</sup> d(OH-OL) |          | 3.0<br>20    |          | ns    |

| $(C_L = 195 pF) A0 thru A15 to Z0, Z1, Z2$<br>$(C_L = 30 pF) A0 thru A15, R/W to S0, S1$                                                              |                            | t <sub>d(A-Z)</sub>                            | <u> </u> | 28<br>18     |          |       |

| (C <sub>L</sub> = 95 pF) Oscillator-Out (C <sub>L</sub> = 95 pF) Oscillator-Out (T <sub>L</sub> to RASO)                                              |                            | td(OL-R0H)                                     | <u>-</u> | 20<br>18     |          |       |

| (C <sub>L</sub> = 95 pF) Oscillator-Out (C <sub>L</sub> = 95 pF) Oscillator-Out (C <sub>L</sub> = 95 pF) Oscillator-Out (C <sub>L</sub> = 95 pF)      |                            | td(OL-R1H)<br>td(OL-R1L)                       |          | 22<br>20     | _        |       |

| (C <sub>L</sub> = 195 pF) Oscillator-Out ¬L to CAS → (C <sub>L</sub> = 195 pF) Oscillator-Out ¬L to CAS ¬                                             | (<br>L                     | td (OL-CH)                                     | _        | 20<br>20     | _        |       |

| (C <sub>L</sub> = 195 pF) Oscillator-Out <sup>¬</sup> L to <del>WE</del> → (C <sub>L</sub> = 195 pF) Oscillator-Out <sup>¬</sup> L to <del>WE</del> → | <u>(</u>                   | t <sub>d</sub> (OL-WH)                         |          | 22<br>40     | _        |       |

| (C <sub>L</sub> = 100 pF) Oscillator-Out <sup>¬</sup> L to E <u>√</u><br>(C <sub>L</sub> = 100 pF) Oscillator-Out <sup>¬</sup> L to E <sup>¬</sup> L  |                            | td(OL-EH)                                      |          | 55<br>25     | _        |       |

| (C <sub>L</sub> = 100 pF) Oscillator-Out  to Q                                                                                                        |                            | td(OL-QH)                                      |          | 55<br>25     | <u> </u> |       |

| (C <sub>L</sub> = 30 pF) Oscillator-Out of to VClk of (C <sub>L</sub> = 30 pF) Oscillator-Out of to VClk                                              |                            | t <sub>d</sub> (OH-VH)                         |          | 50<br>65     | <u> </u> |       |

| (C <sub>L</sub> = 195 pF) Oscillator-Out <sup>¬</sup> L to Row A<br>(C <sub>L</sub> = 195 pF) Oscillator-Out <sup>¬</sup> L to Colum                  |                            | td(OL-AR)<br>td(OL-AC)                         |          | 36<br>33     |          |       |

| (C <sub>L</sub> = 15 pF) Oscillator-Out  to DA0                                                                                                       | Earliest (1)<br>Latest (1) | <sup>t</sup> d(OL-DH)<br><sup>t</sup> d(OL-DH) | _        | – 15<br>+ 15 | _        |       |

| $(C_L = 95 \text{ pF on } \overline{RAS}, C_L = 195 \text{ pFon } \overline{CAS})$                                                                    | AS to RAS                  | td(CL-RH)                                      |          | 208          |          |       |

| Setup Time for A0 thru A15, R/W                                                                                                                       | Rate = ÷ 16<br>Rate = ÷ 8  | t <sub>su(A)</sub>                             |          | 28<br>28     |          | ns    |

| Hold Time for A0 thru A15, R/W                                                                                                                        | Rate = ÷ 16<br>Rate = ÷ 8  | <sup>t</sup> h(A)                              |          | 30<br>30     | _        | ns    |

| Width of HS Low 2                                                                                                                                     |                            | twL(HS)                                        | 2.0      | 5.0          | 6.0      | μs    |

Notes: 1. When using the SAM with an MC6847, the rising edge of DA0 is confined within the range shown in the timing diagrams (unless the synchronizing process is incomplete.) The synchronization process requires a maximum of 32 cycles of OscOut for completion.

2. tWL(HS) wider than 6.0  $\mu s$  may yield more than 8 sequential refresh addresses.

## FIGURE 1 — PROPAGATION DELAY TIMES versus LOAD CAPACITANCE

#### PIN DESCRIPTION TABLE

|            |                         | Name                                         | No.                                          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Power                   | V <sub>CC</sub><br>Gnd                       | 40<br>20                                     | Apply $\pm$ 5 volts $\pm$ 5%. SAM draws less than 230 mA. Return Ground for $\pm$ 5 volts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Input Pins | Control                 | A15<br>A14<br>A13<br>A12<br>A11<br>A10<br>A9 | 36<br>37<br>38<br>39<br>1<br>2               | Most Significant Bit.  MPU address bits A0-A15. These 16 signals come directly from the MPU and are used to directly address up to 64K memory locations or to indirectly address up to 96K memory locations. (See pages 17 and 18 for memory maps). Each input is approximately equivalent to one low power Schottky load.                                                                                                                                                                                                                                                                                                                                                 |

|            | MPU Address and Control | A8<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2       | 24<br>23<br>22<br>21<br>19<br>18             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                         | A0                                           | 16                                           | Least Significant Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            |                         | R/W                                          | 15                                           | MPU READ or WRITE. This signal comes directly from the MPU and is used to enable writing to the SAM control register, dynamic RAM (via WE), and to enable device select #0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            |                         | Oscin                                        | 5                                            | Apply 14.31818* MHz crystal and 2.5-30 pF trimmer to ground. See page 12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | VDG<br>Control          | DA0<br>HS                                    | 9                                            | Display Address DA0. The primary function of this pin is to input the least significant bit of a 16-bit video display address. The more significant 15-bits are outputs from an internal 15-bit counter which is clocked by DA0. The secondary function of this pin is to indirectly input the logic level of the VDG "FS" (field synchronization pulse) for vertical video address updating. Horizontal Synchronization. The primary function of this pin is to detect the falling edge of VDG "HS" pulse in order to initiate eight dynamic RAM refresh cycles. The secondary function is to reset up to 4 least significant bits of the internal video address counter. |

|            |                         | VCIk                                         | 7                                            | VDG Clock. The primary function of this pin is to <b>output</b> a 3.579545 MHz square wave** to the VDG "Clk" pin. The secondary function resets the SAM when this VClk pin is pulled to logic "0" level, acting as an <b>input</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            |                         | Oscout                                       | 6                                            | Apply 1.5 k $\Omega$ resistor to 14.31818* MHz crystal and 33 pF capacitor to ground. See page 12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | Device<br>Selects       | S2<br>S1                                     | 25<br>26                                     | Most Significant Bit (Device Select Bits). The binary value of S2, S1, S0 selects one of eight "chunks" of MPU address space (numbers 0 through 7). Varying in length, these "chunks" provide efficient memory mapping for ROMs, RAMs, Input/Output devices, and MPU Vectors. (Requires 74LS 138-type demultiplexer).                                                                                                                                                                                                                                                                                                                                                      |

| Pins       | MPU<br>Clocks           | S0<br>E                                      | 14                                           | Least Significant Bit.  E (Enable Clock) "E" and "Q" are 90° out of phase and are both used as MPU clocks for the MC6809E. For the MC6800 and MC6801E, only "E" is used. "E" is also used for many MC6800 peripheral chips.  Q (Quadrature Clock).                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Output P   | RAM<br>Address          | Z7† Z6† Z5† Z4† Z3† Z2† Z1† Z0†              | 35<br>34<br>33<br>32<br>31<br>30<br>29<br>28 | Most Significant Bit First, the least significant address bits from the MPU or "VDG" are presented to Z0–Z5 (4K x 1 RAMs) or Z0–Z6 (16K x 1 RAMs) or Z0–Z7 (64K x 1 RAMs). Next, the most significant address bits from the MPU or "VDG" are presented to Z0–Z5 (4K x 1 RAMs) or Z0–Z6 (16K x 1 RAMs) or Z0–Z7 (64K x 1 RAMs). Note that for 4K x 1 and 16K x 1 RAMs, Z7 (Pin 35) is not needed for address information. Therefore, Pin 35 is used for a second row address select which is labeled (RAS1).  Least Significant Bit.                                                                                                                                        |

|            | RAM<br>Control          | RAS1†                                        | 35<br>12                                     | Row Address Strobe One. This pulse strobes the least significant 6,7 or 8 address bits into dynamic RAMs in Bank #1.  Row Address Strobe Zero. This pulse strobes the least significant 6,7 or 8 address bits into dynamic RAMs in Bank #0.  Column Address Strobe. This pulse strobes the most significant 6,7 or 8 address bits into                                                                                                                                                                                                                                                                                                                                     |

|            | ပ                       | CAS†<br>WE†                                  | 11                                           | dynamic RAMs.  Write Enable. When low, this pulse enables the MPU to write into dynamic RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

<sup>\*14.31818</sup> MHz is 4 times 3.579545 MHz television color subcarrier. Other frequencies may be used. (See page 12.)

<sup>†</sup> Due to fast transitions, ferrite beads in series with these outputs may be necessary to avoid high frequency (≈ 60 MHz) resonances.

<sup>\*\*</sup>When VDG and SAM are not yet synchronized the "square wave" will stretch (see page 10.)

#### THEORY OF OPERATION

#### Video or No Video

Although the SAM may be used as a dynamic RAM controller **without** a video display\*, most applications are likely to include a MC6847 video display generator (VDG). Therefore, this document emphasizes use of the SAM with MC6847 systems.

#### Shared RAM (with interleaved DMA)

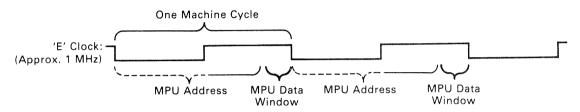

To minimize the number of RAM and interface chips, both the MPU and VDG share common dynamic RAM. Yet, the use of common RAM creates an apparent difficulty. That is, the MPU and VDG must both access the RAM without contention. This difficulty is overcome by taking advantage of the timing and architecture of Motorola MPU's (MC6800, MC6801E, MC6809E, MC68000). Specifically, **all** MPU accesses of external memory **always** occur in the **latter half** of the machine cycle, as shown below:

#### FIGURE 11 - MOTOROLA MPU TIMING

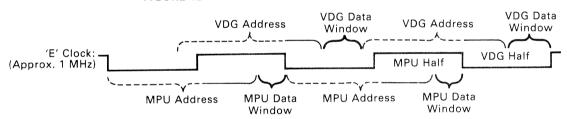

Similarly, the MC6847 (non-interlaced) VDG transfers a data byte in a half machine cycle (E or  $\Phi$ 2). Thus, when properly positioned, VDG and MPU RAM accesses interleave without contention as shown below:

#### FIGURE 12 - MOTOROLA MPU WITH VDG TIMING

This Interleaved Direct Memory Access (IDMA) is synchronized via the MC6883 by centering the VDG data window half-way between MPU data windows.\*\*

The result is a shared RAM system without MPU/VDG RAM access contention, with both MPU and VDG running uninterrupted at normal operating speed, each transparent to the other.

#### **RAM Refresh**

Dynamic RAM refresh is accomplished by accessing eight\*\*\* sequential row addresses every 64\*\*\* microseconds until all addresses have been accessed. To avoid RAM access contention between REFRESH and MPU, each of the refresh accesses occupies the "VDG half" of the interleaved DMA (IDMA). Furthermore, refresh accesses occur only during the television retrace period (at which time the VDG doesn't need to access RAM).

In summary, the VDG, MPU and SAM's Refresh Counter all transparently access the common dynamic RAM without contention or interruption.

#### Why IDMA?

Use of the interleaved direct memory access results in fast modification to variable portions of display RAM, by the MPU, without any distracting flashes on the screen (due to RAM access contention). In addition, the MPU is not slowed down nor stopped by the SAM; thereby, assuring accurate software timing loops without costly additional hardware timers. Furthermore, additional hardware and software to give "access permission" to the MPU is eliminated since the MPU may access RAM at **any** time.

- \*Only 1 pin, (DA0) out of 40 pins is dedicated to the video display.

- \*\*See VDG synchronization (page 10) for more detail.

- \*\*\*When not using a MC6847, HS may be wired low for continuous transparent refresh.

#### **MPU Rate**

Two bits (R1, R0) control the clock rate to the MC6809E MPU. The options are:

| RATE (FREQUENCY OF "E" CLOCK)           | R1   | R0 |

|-----------------------------------------|------|----|

| 0.9 MHz (Crystal Frequency ÷ 16) Slow   | 0    | 0  |

| 0.9/1.8 MHz (Address Dependent Rate)    | 0    | 1  |

| 1.8 MHz (Crystal Frequency ÷ 8) Fast    | 1    | X  |

|                                         |      |    |

| (Typical Crystal Frequency = 14.31818 M | IHz) |    |

In the "address dependent rate" mode, accesses to \$0000-\$7FFF and \$FF00-\$FF1F are slowed to 0.9 MHz (crystal frequency  $\div$  16) and all other addresses are accessed at 1.8 MHz (crystal frequency  $\div$  8).

Note: "Slow" (0.9 MHz) operation can be accomplished using 1.0 MHz MC6809E and MC6821 devices. For "Fast" (1.8 MHz) operation, 2.0 MHz MC68B09E and MC68B21 devices must be used.

#### **Memory Size**

Two bits (M1 and M0) determine RAM memory size. the options are:

| SIZE                                          | M1 | Mo |

|-----------------------------------------------|----|----|

| One or two banks of 4K x 1 dynamic RAMs       | 0  | 0  |

| One or two banks of 16K x 1 dynamic RAMs      | 0  | 1  |

| One bank of 16K x 4 dynamic RAMs <sup>①</sup> | 0  | 1  |

| One bank of 64K x 1 dynamic RAMs              | 1  | 0  |

| Up to 64K static RAM*                         | 1  | 1  |

<sup>1)</sup> This option is only available when using the LS785.

### **IMPORTANT!**

Note: Be sure to program the SAM for the correct memory size before using RAM (i.e., for a subroutine stack).

#### Map Type

One bit (TY) is used to select between two memory map configurations.

Refer to Figures 14–16 for details. Early versions of the LS783 did not allow the "Fast" MPU rate to be used in conjunction with Map Type "TY = 1." Devices manufactured after January 1, 1983 allow both "Fast" and "Slow" MPU rates to be used with Map Type "TY = 1." (Date of manufacture is marked on devices as YYWW where YY is the year and WW is the week of manufacture).

#### Writing To The SAM Control Register

Any bit in the control register (CR) may be set by writing to a specific unique address. Each bit has two unique addresses . . . writing to the **even** # address **clears** the bit and writing to the **odd** # address **sets** the bit. (Data on the data bus is irrelevant in this procedure.) The specific addresses are tabulated in Figures 14–16.

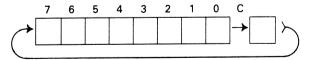

If desired, a short routine may be written to program the SAM CR "a word at a time." For example, the following routine copies "B" bits from "A" register to SAM CR addresses beginning with address "X."

| SAM1 | 46 |    | ROR | Α         |  |

|------|----|----|-----|-----------|--|

|      | 24 | 06 | BCC | SAM2      |  |

|      | 30 | 01 | INX | (LEAX1,X) |  |

|      | A7 | 80 | STA | O,X+      |  |

|      | 20 | 02 | BRA | SAM3      |  |

| SAM2 | A7 | 81 | STA | O,X + +   |  |

| SAM3 | 5A |    | DEC | В         |  |

|      | 26 | F2 | BNE | SAM1      |  |

|      | 39 |    | RTS |           |  |

|      |    |    |     |           |  |

<sup>\*</sup> Requires a latch for demultiplexing the RAM address.

#### FIGURE 14 — MEMORY MAP (TYPE #0)

#### Abbreviations:

M.S. ≡ Most Significant

L.S. = Least Significant

$S \equiv Set Bit$

(All bits are cleared when SAM is reset.) C ≡ Clear Bit

$S \equiv Device Select value = 4 x S2 + 2 x S1 + 1 x S0$

\*On LS785, S = 7 if  $R/\overline{W} = 0$

\*\*This memory area may also be RAM. However, locations \$FFE0-\$FFFF must be ROM when using LS785.

#### FIGURE 15 - LS783 MEMORY MAP (TYPE #1 64K RAM)

Abbreviations:

M.S. = Most Significant

L.S. ≡ Least Significant

S ≡ Set Bit

(All bits are cleared when SAM is reset.)

C = Clear Bit

$S \equiv Device Select value = 4 x S2 + 2 x S1 + 1 x S0$

\*S = 0 if  $R/\overline{W}$  = 1

\*\*Decode S2, S1, and S0 with an open collector SN74LS156 and 'wire-or' state 7 with state 2. (See Appendix B for suggested decode circuit.)

\*\*\*To avoid ROM enable during R/W = LOW, the ROM at S = 2 must be gated with  $R/\overline{W}$ . (See Appendix B for suggested decode circuit.)

#### FIGURE 17 — MEMORY ALLOCATION TABLE

(Also, see the memory MAPs on pages 17 and 18.)

Type # 0: (Primarily for ROM based systems)

| Address Range  | Intended Use                                                                            |

|----------------|-----------------------------------------------------------------------------------------|

| \$FFF2 to FFFF | MC6809E Vectors: Reset, NMI, SWI, IRQ, FIRQ, SWI2, SWI3.                                |

| FFE0 to FFF1   | Reserved for future MPU enhancements.                                                   |

| FFC0 to FFDF   | SAM Control Register: V0, - V2, F0 - F6, P, R0, R1, M0, M1, TY.                         |

| FF60 to FFBF   | Reserved for future control register enhancements.                                      |

| FF40 to FF5F   | I/O <sub>2</sub> : Input/Output (PIAs, ACIAs, etc.) To subdivide, use A0 – A4.          |

| FF20 to FF3F   | I/O <sub>1</sub> : Input/Output (PIAs, ACIAs, etc.) To subdivide, use A0 – A4.          |

| FF00 to FF1F   | I/O <sub>0</sub> : Input/Output (PIAs, ACIAs, etc.) To subdivide, use A0 – A4.          |

| C000 to FEFF   | ROM2: 16K addresses. External cartridge ROM*.                                           |

| A000 to BFFF   | ROM1: 8K addresses. Internal ROM*. Note that MC6809E vector addresses select this ROM*. |

| 8000 to 9FFF   | ROM0: 8K addresses. Internal ROM*.                                                      |

| 0000 to 7FFF   | RAM: 32K addresses. RAM shared by MPU and VDG.                                          |

<sup>\*</sup>Not restricted to ROM. For example, RAM or I/O may be used here.

Type # 1: (Primarily for RAM based systems)

| Address Range  | Intended Use                                                                                                     |

|----------------|------------------------------------------------------------------------------------------------------------------|

| \$FFF2 to FFFF | MC6809E Vectors: Reset, NMI, SWI, IRQ, FIRQ, SWI2, SWI3.                                                         |

| FFE0 to FFF1   | Reserved for future MPU enhancements.                                                                            |

| FFC0 to FFDF   | SAM Control Register: V0 - V2, F0 - F6, P, R0, R1, M0, M1, TY.                                                   |

| FF60 to FFBF   | Small ROM: Boot load program and initial MC6809 vectors.                                                         |

| FF40 to FF5F   | I/O2: Input/Output (PIAs, ACIAs, etc.) To subdivide, use A0 – A4.                                                |

| FF20 to FF3F   | I/O1: Input/Output (PIAs, ACIAs, etc.) To subdivide, use A0 – A4.                                                |

| FF00 to FF1F   | I/O1: Input/Output (PIAs, ACIAs, etc.) To subdivide, use A0 – A4.                                                |

| 0000 to FEFF   | RAM: 64K(-256) addresses, shared by MPU and VDG.                                                                 |

| 0000 to 1211   | (If $R\overline{W} = 0$ then $S = 3$ for \$C000-\$FEFF; $S = 2$ for \$A000-\$BFFF; $S = 1$ for \$8000-\$9FFF and |

|                | S = 7 for \$0000-\$7FFF.)                                                                                        |

#### Preliminary

#### **DESCRIPTION**

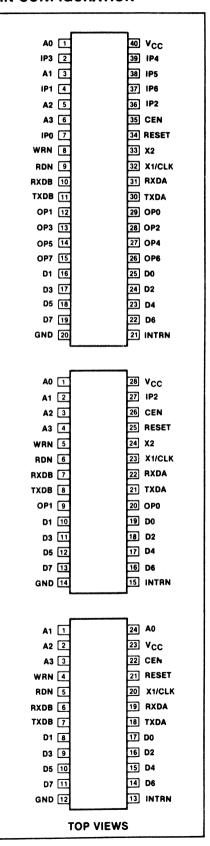

The Signetics SCN2681 Dual Universal Asynchronous Receiver/Transmitter (DUART) is a single chip MOS-LSI communications device that provides two independent full-duplex asynchronous receiver/transmitter channels in a single package. It interfaces directly with microprocessors and may be used in a polled or interrupt driven system.

The operating mode and data format of each channel can be programmed independently. Additionally, each receiver and transmitter can select its operating speed as one of eighteen fixed baud rates, a 16x clock derived from a programmable counter/timer, or an external 1x or 16x clock. The baud rate generator and counter/timer can operate directly from a crystal or from external clock inputs. The ability to independently program the operating speed of the receiver and transmitter make the DUART particularly attractive for dual-speed channel applications such as clustered terminal systems.

Each receiver is quadruply buffered to minimize the potential of receiver overrun or to reduce interrupt overhead in interrupt driven systems. In addition, a flow control capability is provided to disable a remote DUART transmitter when the buffer of the receiving device is full.

Also provided on the SCN2681 are a multipurpose 7-bit input port and a multipurpose 8-bit output port. These can be used as general purpose I/O ports or can be assigned specific functions (such as clock inputs or status/interrupt outputs) under program control.

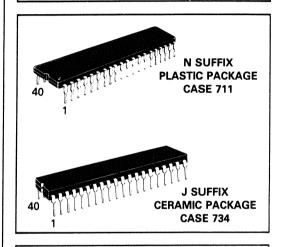

The SCN2681 is available in three package versions to satisfy various system requirements: 40-pin and 28-pin, both 0.6" wide DIPs, and a compact 24-pin, 0.4" wide, DIP.

#### **FEATURES**

- Dual full-duplex asynchronous receiver/ transmiter

- Quadruple buffered receiver data registers

- · Programmable data format

1/16 bit increments

- -5 to 8 data bits plus parity

- Odd, even, no parity or force parity1, 1.5 or 2 stop bits programmable in

- Programmable baud rate for each receiver and transmiter selectable from:

- -18 fixed rates: 50 to 38.4K baud

- —One user defined rate derived from programmable timer/counter

- -External 1x or 16x clock

- Parity, framing, and overrun error detection

- · False start bit detection

- · Line break detection and generation

- Programmable channel mode

- -Normal (full duplex)

- -Automatic echo

- -Local loopback

- -Remote loopback

- Multi-function programmable 16-bit counter/timer

- Multi-function 7-bit input port

- -Can serve as clock or control inputs

- —Change of state detection on four inputs

- Multi-function 8-bit output port

- -Individual bit set/reset capability

- Outputs can be programmed to be status/interrupt signals

- · Versatile interrupt system

- Single interrupt output with eight maskable interrupting conditions

- Output port can be configured to provide a total of up to six separate wire-OR'able interrupt outputs

- Maximum data transfer: 1X 1MB/sec, 16X — 125KB/sec

- Automatic wake-up mode for multidrop applications

- Start-end break interrupt/status

- Detects break which originates in the middle of a character

- On-chip crystal oscillator

- TTL compatible

- Single + 5V power supply

#### ORDERING CODE

| BA0//4050                  | $V_{CC} = 5V \pm 5\%$ , $T_A = 0^{\circ}C$ to $70^{\circ}C$ |                                |                     |  |  |

|----------------------------|-------------------------------------------------------------|--------------------------------|---------------------|--|--|

| PACKAGES                   | 24 Pin <sup>1</sup>                                         | 28 Pin²                        | 40 Pin <sup>2</sup> |  |  |

| Ceramic DIP<br>Plastic DIP | Not available<br>SCN2681AC1N24                              | SCN2681AC1128<br>SCN2681AC1N28 |                     |  |  |

<sup>1400</sup> mil wide DIP

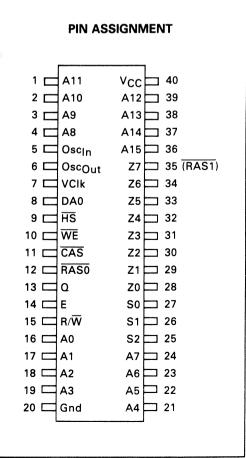

#### PIN CONFIGURATION

<sup>&</sup>lt;sup>2</sup>600 mil wide DIP

#### Preliminary

#### **BLOCK DIAGRAM**

### Preliminary

### PIN DESIGNATION

|          | APPLICABLE |    | TYPE | NAME AND FUNCTION |                                                                                                                                                                                                                                                         |  |  |  |  |  |

|----------|------------|----|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MNEMONIC | 40         | 28 | 24   | ITPE              | PE NAME AND FUNCTION                                                                                                                                                                                                                                    |  |  |  |  |  |

| D0-D7    | х          | Х  | X    | 1/0               | Data Bus: Bidirectional 3-state data bus used to transfer commands, data and status between the DUART and the CPU. Do is the least significant bit.                                                                                                     |  |  |  |  |  |

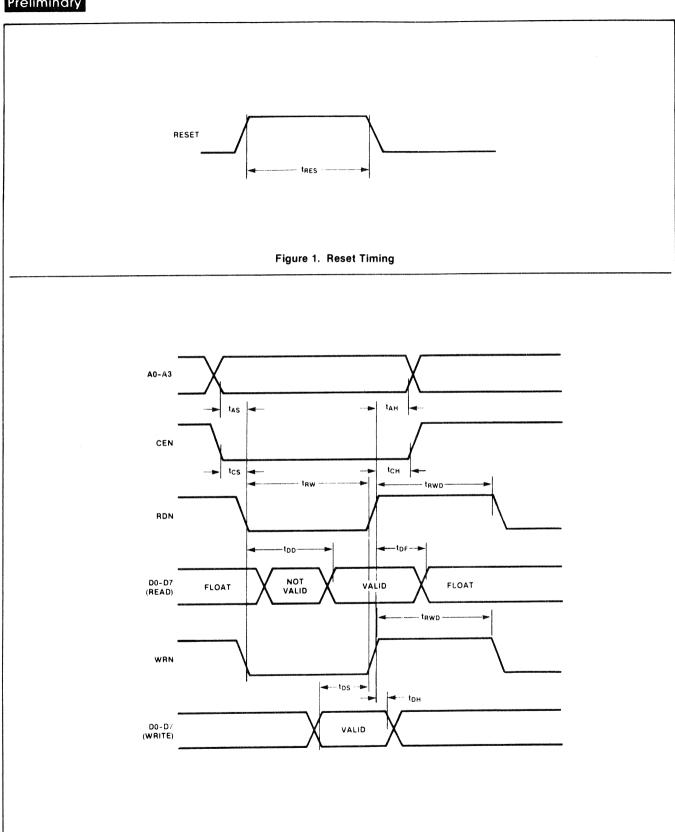

| CEN      | ×          | x  | x    | 1                 | Chip Enable: Active low input signal. When low, data transfers between the CPU and the DUART are enabled on D0-D7 as controlled by the WRN, RDN and A0-A3 inputs. When high places the D0-D7 lines in the 3-state condition.                            |  |  |  |  |  |

| WRN      | х          | x  | x    | ı                 | Write Strobe: When low and CEN is also low, the contents of the data bus is loaded into the addressed register. The transfer occurs on the rising edge of the signal.                                                                                   |  |  |  |  |  |

| RDN      | х          | x  | x    | ı                 | Read Strobe: When low and CEN is also low, causes the contents of the addressed register to be presented on the data bus. The read cycle begins on the falling edge of RDN.                                                                             |  |  |  |  |  |

| A0-A3    | ×          | x  | ×    | 1                 | Address Inputs: Select the DUART internal registers and ports for read/write operations.                                                                                                                                                                |  |  |  |  |  |

| RESET    | x          | x  | ×    | 1                 | Reset: A high level clears internal registers (SRA, SRB, IMR, ISR, OPR, OPCR), puts OP0-OP7 in the high state, stops the counter/timer, and puts channels A and B in the inactive state with the TxDA and TxDB outputs in the mark (high) state.        |  |  |  |  |  |

| INTRN    | x          | x  | x    | 0                 | Interrupt Request: Active low, open drain, output which signals the CPU that one or more of the eight maskable interrupting conditions are true.                                                                                                        |  |  |  |  |  |

| X1/CLK   | ×          | x  | ×    | ı                 | Crystal 1: Crystal or external clock input. A crystal or clock of the specified limits must be supplied at all times. When a crystal is used, a capacitor must be connected from this pin to ground (see figure 5).                                     |  |  |  |  |  |

| X2       | х          | ×  |      | 0                 | <b>Crystal 2:</b> Connection for other side of the crystal. Should be connected to ground if a crystal is not used. When a crystal is used, a capacitor must be connected from this pin to ground (see figure 5).                                       |  |  |  |  |  |